Transistor Puzzles

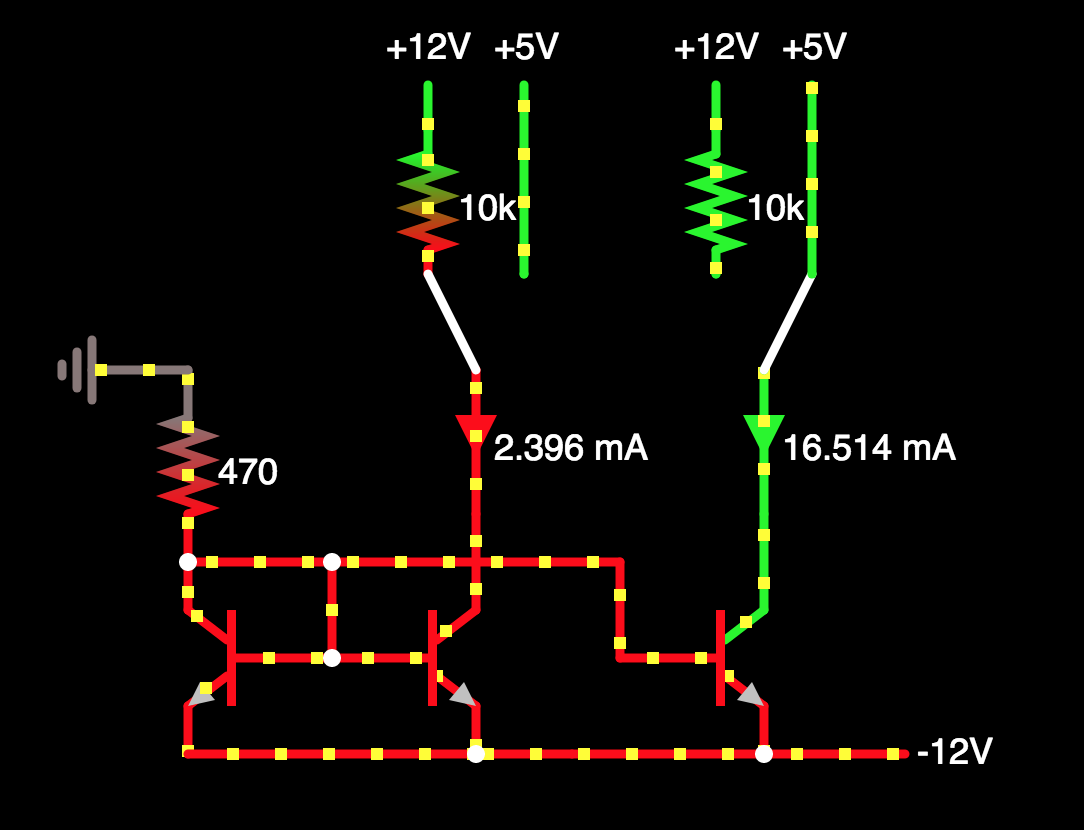

I’ve fallen into a deep hole involving current-limiting circuits and current sources, in an attempt to solve a minor problem with the Yellowstone disk controller. In the big scheme of things, this isn’t a very important problem, but it has me intrigued. I’ve created a simulation of a circuit that may solve the problem, but it exhibits some transistor behavior that I don’t understand. Specifically, the base currents of the transistors don’t seem to follow the rules that I thought I understood.

You can see a working simulation of the circuit here.

The are two SPDT switches at the top of the diagram, representing Yellowstone’s two disk connectors. On pin 9 of this connector, some types of drives will have a 10K resistor connected to the +12V supply. This type of drive needs a -12V supply input on pin 9. It will use about 3 mA at most from -12V. Other types of drives will have a direct connection to +5V on pin 9 (+5V is also provided on pin 11 to all drive types). Yellowstone can either provide an additional +5V supply on pin 9 for this type of drive, or more simply, just leave the pin unconnected.

The basic idea here is to establish a current limiter of about 10-20 mA for pin 9. That’s more than enough for normal operation with the -12V supply, and it prevents dangerously high amounts of current flowing if -12V is directly connected to +5V as in the second type of drive.

Here’s the puzzle: the three NPN transistors have all their bases connected, and all their emitters connected. As shown, they all have the same base-emitter voltage Vbe of 0.668 volts. My mental model is that the base-emitter connection is essentially like a diode. With identical diodes, identical Vbe, and a single shared 470 ohm current-limiting resistor, I would expect the base current Ib to be identical for all three transistors. Yet they’re not. The middle transistor’s Ib is 7.2 mA while the others are only 0.165 mA.

The fact that one transistor is in saturation must be relevant. But the “base-emitter connection is a diode” assumption is failing here, and I can’t explain why. I need to read more transistor theory.

Read 13 comments and join the conversation13 Comments so far

Leave a reply. For customer support issues, please use the Customer Support link instead of writing comments.

That simulation uses ideal voltage sources, right? Their source impedance is exactly zero. That’s not how the real world works. A real-world computer power supply has a source impedance in the milliohms range. So your simulation already starts with unrealistic parameters.

Also, your current mirror is very basic, with a lot of room for improvements: https://wiki.analog.com/university/courses/electronics/text/chapter-11

For a practical current mirror, you want good thermal coupling between the transistors, and the transistors should be very similar. There are ICs containing usable current mirrors, sometimes using two transistors in a single (SMD) case may be sufficient.

You’re right about those shortcomings. Does that explain the confusing behavior of the middle transistor? All three transistors have the same Vbe. They’re ideal transistors with identical properties. If base-emitter is modeled like a diode, then shouldn’t identical Vbe mean they will have identical base currents? Why is the base current of one transistor so different than the others? Is that an artifact of the simulation, or some real BJT effect where the collector voltage or current somehow causes a change in the base current?

The current through the transistor on the left is 12/470 = 25mA. So the other transistors are limited to 25mA max, but there is less flowing through them. The center one sees a current of about (12- -12 – Vice)/10E3 = 2.4mA. The actual Vce (seems to be 0.4V) reduces this a little. On the right, it’s current is limited by the Rce, which is controlled by the Vbe, but will not exceed the 25mA set by the Vbe.

Instead of a diode, the model is more like a voltage controlled resistor. The Vbe voltage determines the Rce. Hence the name “transistor” from “transfer resistance “

Steve, David Brown is right.

To clarify a little, IF the transistors are exactly matched, and thermally coupled, THEN, and only then will the currents work out. My calculations show 24.27 mA through the left transistor ((12-0.6)/470). If the transistors are matched, and thermally connected, then the maximum you should be able to pull through one is 24.27mA. You can certainly pull less as the center transistor shows. (24V-0.6)/10,000 = 2.34 mA. Pretty much dead on what the simulation says. I don\\\’t know why the simulation shows only 16 mA through the right transistor. I really would expect a bit more current. But remember in the real world, as a transistor heats up, its Vbe goes DOWN, causing it to hog current. That\\\’s why on most parallel output circuits, you see emitter resistors to balance the current between the transistors. In the case of current mirrors, the transistors have to be matched for Hfe (gain), and thermally connected to keep the Vbe\\\’s the same.

Also, usually, current mirrors use only 2 transistors. I\\\’m not as familiar with 3. That might account for the lower current in the right transistor. David, any thoughts on this?

@David I think you’re describing the collector currents. I’m wondering about the base currents.

## Base currents ##

My sim (QUCS) shows the transistors having the same base current. I am not sure what\’s going wrong in your sim.

http://halestrom.net/misc/otherforums/bmow_transistor_puzzle.png

Note that the third transistor has a slightly different base current: that\’s because it\’s collector & base are not tied. This is normal to see in these current mirror circuits, it\’s only a small error so it\’s often ignored.

## Your circuit has some secretive problems ##

Connecting multiple collectors to bases is unusual, I am not sure why you are doing that. Normally only one transistor has the collector connected to its base (this one sets the reference for everyone else). This leads onto the next problem.

The left 470ohm resistor and the middle 10k resistor are forming a _voltage divider_ because they both connect to the same node. This circuit is no longer a standard current mirror with one-resistor-per-transistor, instead the two left transistors are effectively in parallel. This means the \”mega-transistor\” on the left is no longer matched to the normal transistor on the right, so currents will not match either.

It\’s generally recommended you put some small resistors below each emitter (aka emitter degneration), this improves the match of your current mirror. In your case it might not matter too much (you don\’t need absolute accuracy of your current limit in your application) unless your circuit turns out to suffer thermal runaway (worth testing under worst-case load with a heatgun).

Finally: keep in mind that BJTs are not simple INPUT-PROCESSING-OUTPUT devices like computers. We often simplify them by thinking base=input and collector=output, but in reality if you change the collector conditions (eg by changing a resistor above the collector) then you will see changes at the base too. They\’re often small, but in some circuits even tiny mV deviations at the base can throw things off.

Addendum:

\”_voltage divider_\” -> actually it\’s more complicated than that because the transistors are loading this node down too. The exact behavior of this circuit is not simple to predict without lots of transistor approximation algebra or a simulation. Overall: your circuit shown above isn\’t really a current mirror at all.

\”Finally:\” -> I believe emitter degen resistors also help counteract this.

….and I\’m a total complete numbat. The collector and base of your middle transistor are NOT connected.

PLEASE DISREGARD MOST OF MY ABOVE POSTS :/

Now we return to your regular programming:

https://halestrom.net/misc/otherforums/bmow_transistor_puzzle_FIXED_degennone.png

https://halestrom.net/misc/otherforums/bmow_transistor_puzzle_FIXED_degen10.png

– The 10K resistor is indeed too big. According to my sims it needs to be 1k or less for current regulation to work (red, brown and orange lines on graph).

– Once out of regulation: the base current for the transistor raises dramatically in a futile effort to bring the circuit back into regulation (cyan line that rises well above the rest).

– Emitter degeneration of a few ohms notably improves performance (compare the two images linked), but again is probably only worth considering in your cases for reasons of temperature performance (not simulated in my tests).

The 10K resistor (topR in your schematic) is actually part of the disk drive for some drives, not an independent variable that I can control. It’s the resistance through both terminals of a pot inside the Disk II drive circuitry, where normally the -12V supply should be connected. It’s understandable that the circuit can’t maintain the intended current with a 10K resistor there, and actually it’s exactly what I want. This diagram may help: https://www.bigmessowires.com/wp-content/uploads/2021/07/ys-schematic.png

Yellowstone has two drives connected, of unknown types. As shown in the diagram, in this example, the first drive is a Disk II and the second drive is a bare 3.5 inch drive mechanism. The desired behavior here is to limit the current through any 3.5 inch drives to about 10 mA (the exact value is unimportant), while allowing Disk II drives to use as much current as they possibly can given their 10K internal resistance. Theoretically that would be about 2.4 mA (24V / 10K ohm), but I’d like the circuit to allow some headroom up to 5-10 mA before it begins to limit the current.

> keep in mind that BJTs are not simple INPUT-PROCESSING-OUTPUT devices like computers. We often simplify them by thinking base=input and collector=output, but in reality if you change the collector conditions (eg by changing a resistor above the collector) then you will see changes at the base too.

Yes. Exactly. That’s exactly the crux of the “transistor puzzle” I’ve tried to explain here. And I don’t understand it. All of the BJT discussions that I’ve found on the web say that changing the current through the base-emitter path (and possibly also through the base-collector path) will change the current through the collector-emitter path. Like you say, they describe the transistor as base-emitter is input, collector-emitter is output. They don’t mention any possibility of conditions at the collector somehow altering the base-emitter current. Yet if the sim is to be believed, that’s exactly what’s happening. I’m guessing this is due to some secondary behavior of the transistor that’s normally ignored when doing simple analysis. But what is this secondary behavior, and where can I learn more about it? Is there some formula or rule of thumb that I can use to estimate it? That’s what I’m trying to understand.

If you imagine transistors as being ideal infinite gain devices, but with a small ideal resistor in series with each leg, I think that would make clear what’s going on. Base-emitter voltage is a function of both incoming base current and outgoing emitter current, and the outgoing emitter current will be the sum of the incoming currents on both the base and collector. Reducing the emitter current while keeping the base current equal would reduce the Vbe drop. This will reduce the amount of current flowing into the collector and base of the reference transistor at the left, and the amount of current flowing into the base of the second load transistor. The reference current source which is feeding the mirror, however, will keep delivering the same amount of current, and the excess will have nowhere to go but the base of Q2. This extra current will increase Vbe drop, thus allowing the other transistors to conduct a bit more, until an equilibrium is reached.

A limitation with BJT-based current mirrors is that if one tries to use a single reference transistor with multiple load transistors, the Vbe on the reference may vary in response to overly light loading on some of the load transistors. This won’t matter if the reference transistor is only used with one load (if its VBE is telling the load transistor to accept more current than is available, the exact amount of current that’s being requested won’t matter) but will cause trouble if it’s used with multiple loads. I think a MOSFET-based current mirror could be better in that regard, since gate currents will be independent of loading (since they’re always essentially zero).

Yes, I agree the current-limiting circuit using FETs has several advantages over the circuit with BJTs, and maybe it’s the better solution for this purpose. The only reason I focused on the BJT circuit is that when the Disk II drive is connected (the top-center branch in the circuit), the simulation shows that the approach with BJTs may be able to produce a -12V supply output that’s closer to a true -12V. It shows -11.95V when using BJTs and -11.85V when using FETs. Both are probably close enough, but since the Disk II seems to use -12V as part of an analog reference, I thought it was better to get it as close as possible.

I took some real-world measurements today for this proposed Yellowstone current limiter of the -12V power supply. I measured a Disk II drive using about 2.2 mA from this supply, which is just about where I had predicted. For a sanity check, I disconnected the -12V supply, and disks were no longer readable. Then I connected a 100 ohm resistor between the Disk II drive and the -12V supply, which should produce a 0.22 V shift in the voltage seen by the drive. Everything still worked OK, which tells me the -12V supply doesn’t need to be super precise.